# Department of Electronics and Communication Engineering

Report of

Value added course on

"Digital Design Using Verilog"

From 19/02/2019 to 23/02/2019

**Organized**

In collaboration with IETE

by

Mr.Bavusaheb B Kunchanur

Assistant Professor

Dept of ECE

**KGRCET**

Mr. A Vijaya Bhasker Reddy

**Assistant Professor**

Dept of ECE

**KGRCET**

COORDINATOR

HOD

DEFT. OF ELECTRONICS & COMMUNICATIONS ENGINEERING K.G. REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

CHILKUR (Y) MOIMABAD, R.R. DIST. 501 804.

PRINCIPAL

R.R.Dist., Telangana.

#### SUMMARY REPORT DIGITAL DESIGN USING VERILOG

#### **About Course**

Fundamental of Designers can develop an executable functional specification that documents the exact behaviour of all the components and their interfaces Designers can make decisions about cost, performance, power, and area earlier in the design process — Designers can create tools which automatically manipulate the design for verification, synthesis, optimization, etc. Hardware description languages are an essential part of modern digital design.

- HDLs can provide an executable functional specification.

- HDLs enable design space exploration early in design process.

- HDLs encourage the development of automated tools.

- HDLs help manage complexity inherent in modern designs.

#### Scope of the Course

As designs grew larger and more complex, designers began using gate-level models described in a Hardware Description Language to help with verification before fabrication When designers began working on 100,000 gate designs, these gate-level models were too lowlevel for the initial functional specification and early high-level design exploration.

#### Objectives of the course

Designers again turned to HDLs specification and a framework for help – abstract behavioural models written in an HDL provided both a precise for design exploration Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behaviour from implementation at various levels of abstraction

#### **OUTPUT**

Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behavior from implementation at various levels of abstraction Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behaviour from implementation at various levels of abstraction.

#### The main outputs are mentioned below:

- ❖ The expert shared his knowledge among students.

- Students learned from this course and tried to use the techniques for their project as well as research work.

- Students interact with expert to gain their additional knowledge for future research work.

- Students found new ideas, concept, knowledge on technology, different application of methodologies from different session of course.

- ❖ Department tried to do their collaborative research work on this course with university as well as industries.

- ❖ It was created different domains of research field from this course for possible topic of Electronics and communication Engineering.

- . It helped to make industrial project.

- ❖ It helped to student for campus recruitment as well as datbase development

### **Summary of Participants**

- (a) Number of students attended this course: 5 52

- (b) Number of students certified: 352

## DAY-1:

In the first session students got familiar with Hardware description language and been explained by the expertise. The session was interesting and students run small practical using Xilinx they implemented some circuits on system with simulation.

Introduction to Digital Design Using Verilog

In the beginning designs involved just a few gates, and thus it was possible to verify these circuits on paper or with breadboards As designs grew larger and more complex, designers began using gate-level models described in a Hardware Description Language to help with verification before fabrication so different experiments were done using verilog,VHDL programs with the help of expertees.

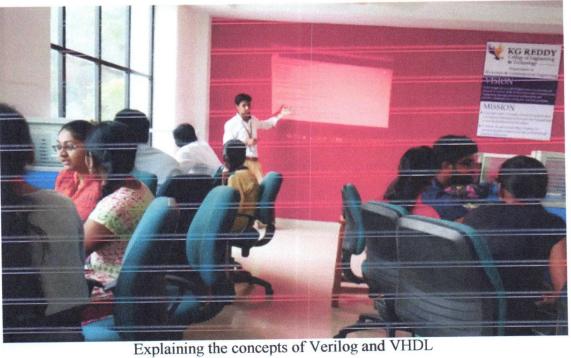

Explaining about different logic circuits

The following topics have been covered on day 3 that is on Current Trends and role of Programmable logic devices in VLSI Design Industry

- Digital Design concepts & implementation

- Verilog concepts

- Different Modelling styles used in Verilog

- DUT verification by simulation using Directed Test benches

- Synthesizable coding targeted to Xilinx devices

- FPGA Architecture basics

- ASIC & FPGA Design flow

- Synthesis and FPGA Implementation

Different Modelling styles used in Verilog used by students

The day 4 was on Digital Design using Logic works following topics have been covered

- Xilinx ISE software for writing HDL codes

- Verifying the HDL codes by writing Testbenches using ISim (Xilinx ISE)

- Synthesis of HDL codes on Xilinx FPGA Kits

- IPCoregen flow

- Xilinx ISE Design flow

- Chipscope Pro flow

- List of FPGA Practicals –Full Adder, Ripple-carry Adder, DFF, Counters, Shifters, ALU, RAM/ROM etc..

Xilinx ISE software for writing IIDL codes and various activity carried out by students

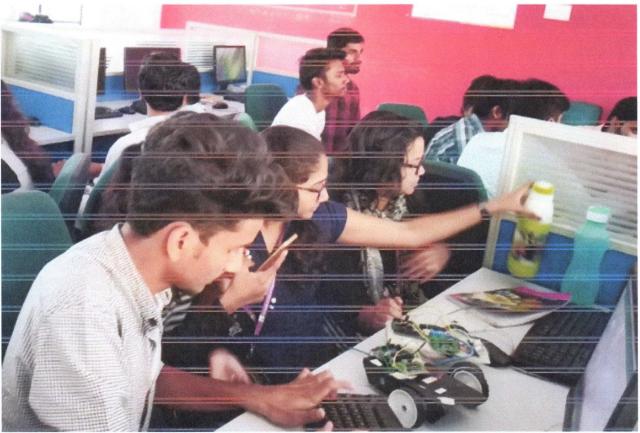

On the final day Software & Boards Specification and hands on session was carried out by students.

- Logic works 5.0

- Xilinx ISE 14.2 and its associated Tool chain

- Xilinx Spartan 3 and 6 FPGA Development kits

Participants got hands-on experience on Digital Logic Design concepts and implementation, Verilog basics and understanding the powerful features of the language. Participants also got introduced to ASIC vs. FPGA Design flows. They were introduced with the concepts of FPGA internal architecture and finally they also got exposure to the FPGA design flow by themselves synthesizing their own HDL codes into the various development kits from Xilinx.

Participants also got hands on experience for using the Xilinx IP's provided as a part of package in their design

Students solving realtime problems In the last session, we have conducted a test to evaluate and certify the students At 4:15pm Prof. M.N.Narsaiah, HOD,ECE, KGRCET issued the certificates. He concluded by addressing the students and explained the motive behind the Course. He suggested the students to do their mini, major projects on Arduino and IoT with the help of faculty members.

Ref No: KGRCET/ECE/2018-19

CIRCULAR

Date 16 /2/2019

All the students of II-B.Tech II semester ECE are here by instructed to enroll for the value added course on "**Digital Design Using Verilog**", which is going to conduct from 19/02/2019 to 23/02/2019. Interested students are instructed to meet co ordinator

HOD

HEAD

REPT. OF ELECTRONICS & COMMUNICATIONS ENGINEERING R.G. REDDY COLLEGE OF ENGINEERING & TECHNOLOGY CHIRCUM (V). MOMMARAD, R.R. OKST501 80%. Principal

Principal

KG Reddy College of Engineering & Technology

Chilkur (V), Moinabad (M).

R.R.Dist., Telangana.

# Syllabus for Digital design using Verilog Introduction to Digital design using Verilog Verilog HDL

- Evolution of Computer Aided Digital Design

- Evolution and Importance of Hardware

Description Language (HDL)

• VLSI Design Flow

### **Basic Concepts of Verilog HDL**

- Hierarchical modeling concepts

- Lexical Conventions

- Data Types

- System Tasks and Compiler Directives

- Modules and Ports

### Finite State Machine (FSM)

- Introduction to FSM

- State Machine Models and Presentations

- Transition Matrix

- State Transition Diagram

- Moore and Mealy Model

- State Transition Table

Gate Level Modeling

- Gate Types

- Array of Instances

- Gate Delays

- •Writing a test bench

- Gate level modeling of various digital circuits

# **Data flow Modelling**

- Continuous Assignments

- Delays

- Operators

- Data Flow modeling of various digital circuits

# **Behavioural Level Modelling**

- Structured Procedures

- Procedural Assignments

- Timing Control

- Conditional Statements

- Multiway Branching

- Loops

- Sequential and Parallel Blocks

#### KG REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

#### Attendance Sheet for value added course on Digital Design using Verilog

#### Class:II-II ECE

Date:19/02/2019-23/02/2019

| Class:11-11 ECE Date:19/02/2019-23 |            |                          |           |         | /02/2019 |        |           |  |  |

|------------------------------------|------------|--------------------------|-----------|---------|----------|--------|-----------|--|--|

| SI.No.                             | Roll No    | Name of the Student      | Signature |         |          |        |           |  |  |

|                                    | 7          |                          | 19        | 20      | 21       | 22     | 23        |  |  |

| 1                                  | 16QM1A0405 | CHINNAPEESARI SNEHA      | 0         | Sur     | Sie      | See    | Su        |  |  |

| 2                                  | 17QM1A0401 | A RAMADEVI               | Pay.      | Pay     | By.      | Buy    | Days      |  |  |

| 3                                  | 17QM1A0402 | AADHA KAMALAKAR          | Com       | ( View) | Soul     | Coul   | Court     |  |  |

| 4                                  | 17QM1A0403 | ADLA PRIYANKA            | A-Q-4     | A-Qif   | A fair   | A Day  | FeD.4     |  |  |

| 5                                  | 17QM1A0404 | ALLI GOUTHAMI            | - AND     | AN      | A        | A      | SA        |  |  |

| 6                                  | 17QM1A0405 | ANUGU MAHENDER REDDY     | (ND       | wer     | and      | Much   | over over |  |  |

| 7                                  | 17QM1A0406 | BANDARI DHARANI          | DV        | 6       | \$       | .to    | 4         |  |  |

| 8                                  | 17QM1A0407 | BOKKA KEERTHI REDDY      | Luc       | Lew     | Wee      | , he   | his       |  |  |

| 9                                  | 17QM1A0408 | C SAI DEEKSHA SAGAR      | DUZ-      | Dy      | 18       | 20     | Ta        |  |  |

| 10                                 | 17QM1A0409 | D SWETHA                 | 8         | Su      | 84       | 4      |           |  |  |

| 11                                 | 17QM1A0410 | DANDIGEY VASAVI RANI     | valus     | Valery  | vasaig   | Vasay  | Nasay     |  |  |

| 12                                 | 17QM1A0411 | DEEPAK KUMAR SETH        | Tertes    | Jul     | twel     | 1010   | Durch     |  |  |

| 13                                 | 17QM1A0412 | DHARMISHETTY SAMHITHA    | Sen       | Ju.     | Que      | Soe    | Q         |  |  |

| 14                                 | 17QM1A0413 | DUDDU DILEEP KUMAR       | Dor       | Del     | Del      | Dell   | Dul       |  |  |

| 15                                 | 17QM1A0414 | J KARTĤIK                | Co        | The     | (vOe     | ale    | (All      |  |  |

| 16                                 | 17QM1A0415 | K AJAY REDDY             | Ayay      | Hay     | Ajpu     | Ajay   | ATOU      |  |  |

| 17                                 | 17QM1A0416 | K SAI KRISHNA REDDY      | Can       | oc/     | w        | ho     | G.        |  |  |

| 18                                 | 17QM1A0418 | KADIRA SAI POOJITHA      | Poofs     | YoofUt  | Poofult  | poojib | Poojly    |  |  |

| 19                                 | 17QM1A0419 | KALIKOTA MEGHANA         | Mean      | Megu    | Moju     | Meg    | me        |  |  |

| 20                                 | 17QM1A0420 | KARETI NAGA SURENDRA     | my        | SID     | Told     | 1000   | 182       |  |  |

| 21                                 | 17QM1A0421 | KONDOJU SHIVA SAI CHARAN | Choon     | Olse    | Char     | Chee   | Cho       |  |  |

| 22                                 | 17QM1A0422 | KOWKUNTLA LOKESH REDDY   | Klost     | KLOK    | klob     | Klor   | tobe      |  |  |

| 23                                 | 17QM1A0423 | KUMBAM PAVAN KUMAR       | Poul      | P.      | Re       | Ede    | Q.        |  |  |

| 24                                 | 17QM1A0424 | KUNTALA CHAITANYA KUMAR  | Bue       | Que     | Our      | bu     | in        |  |  |

| 25                                 | 17QM1A0425 | LINGALA SHIVA KUMAR      | Sur       | Ser     | Slu      | Ser    | Cn        |  |  |

| 26                                 | 17QM1A0426 | MALEKEDI SAI RANI        | MBy       | By      | Ry'      | Py     | Ry        |  |  |

| 27                                 | 17QM1A0427 | MANDAPAKA DILIP          | Olly      | Pelif   | Delig    | Dely   | Dalap     |  |  |

| 28                                 | 17QM1A0428 | MEGHRAJ BHANU            | Sha       | any     | Flo      | al     | -31       |  |  |

| 29                                 | 17QM1A0429 | MITTA AKHILA             | ty        | Aus     | Aug      | Ay     | As        |  |  |

| 30 | 17QM1A0430 | MOHAMMED ZUBAIR KHAN     | the       | heu       | Ou       | Ru          | bu       |

|----|------------|--------------------------|-----------|-----------|----------|-------------|----------|

| 31 | 17QM1A0431 | PANTHAM DIVYA            | Duga      | Duya      | Druja    | Danja       | Duya     |

| 32 | 17QM1A0432 | PASUPULA MAHESH          | noh       | poelu     | Iroch    | Moh         | M        |

| 33 | 17QM1A0433 | PUTTA SRAVANTHI          | fry       | Suy       | Ly       | Suy         | dy       |

| 34 | 17QM1A0434 | RAMAVATH RAKESH NAIK     | Kans      | R         |          | Q.          | Roman    |

| 35 | 17QM1A0436 | S LILLY MARGRATE MARY    | tily      | Lilly     | tilly    | tilly       | Lilly    |

| 36 | 17QM1A0437 | S.K GULAM RABBANI        | Rai       | 6d        | Ren      | Bor         | (A)      |

| 37 | 17QM1A0439 | SHIVA KUMAR              | They      | and       | Sho      | Show        | Eli      |

| 38 | 17QM1A0441 | SOMA VIGHNATHA           | Vighnathe | lighouthe | lighnath | * Vighnathe | vighnath |

| 39 | 17QM1A0442 | SUNKARI NIKITHA          | Nolos     | Elin      | Nece     | New         | Ne       |

| 40 | 17QM1A0443 | T SAI CHARAN             | Saidas    | Sada      | -Saidus  | Saidas      | Said     |

| 41 | 17QM1A0444 | TAMMALI VEERESH          | Venes     | Veranex   | Neveres  | reened      | nemy     |

| 42 | 17QM1A0445 | THIMMAPURAM MAMATHA      | Manuello  | namel     | warmit   | nanote      | - namot  |

| 43 | 17QM1A0446 | TIRMAL APURVA            | Africe    | Apri      | April    | Apri        | Am       |

| 44 | 17QM1A0447 | TODUPUNURI AKASH         | ARONSH    | Acoust    | Akalh    | Akarh       | Brown    |

| 45 | 17QM1A0448 | UPPARI DIVYA             | Dioys     | Divya     | Droyer   | Roye        | Orayer   |

| 46 | 17QM1A0449 | VISHWANATH VARANASI      | lon       | bee       | Vae      | Va          | Vce      |

| 47 | 17QM1A0450 | YALALA PAVANI            | Pavas     | Pawary    | Pavonj   | Ravay       | Pavaj    |

| 48 | 17QM1A0451 | MOLTHATI YASHWANTH KUMAR | Hon       | Le        | ye-      | - do        | 4        |

| 49 | 17QM1A0453 | MUHAMMED MUSHARRAF UL H  | AMEED (   | the       | per      | Hei         | We       |

| 50 | 17QM1A0454 | R YASHWANTH              | fre       | You       | ye.      | Luc         | les      |

| 51 | 18QM5A0401 | BANDARI DATTUKUMARI      | Ber       | Today     | Vale     | Taly        | Tale     |

| 52 | 18QM5A0402 | T RISHI RAJ              | Maxh      | Akash     | Akalh    | orah        | Blam     |

| 53 | 17611A0401 | K. Aks Kaya              | Acel      | Acel      | Acal     | Act         | Acel     |

HOD

PRINCIPAL

34) 1760/A0406 G. Ranya

CHIERUS (1), MOIMARD L. W.

Ramyon Ramya Ramya Ramya Roemya

# CERTIFICATE

Name: AADHA KAMALAKAR

Registration No: 17QM1A0402

has successfully completed the prescribed requirements for the award of value added course on "Digital Design Using Verilog" conducted by department of Electronics and Communication Engineering held in month of February from 19/02/2019 to 23/02/2019 in the academic year 2018-2019.

Date: 23-02-2019

Bavu.

**Course Coordinator**

Principal

# CERTIFICATE

Name: ADLA PRIYANKA

Registration No: 17QM1A0403

has successfully completed the prescribed requirements for the award of value added course on "Digital Design Using Verilog" conducted by department of Electronics and Communication Engineering held in month of February from 19/02/2019 to 23/02/2019 in the academic year 2018-2019.

Date: 23-02-2019

Bavu.

**Course Coordinator**

Principal