#### Introduction to Computer Organization

#### **Chapter Outline**

- System Organization

- CPU Organization

- Memory Organization and Interfacing

- I/O Organization and Interfacing

- Relatively Simple Computer

- 8085-based Computer

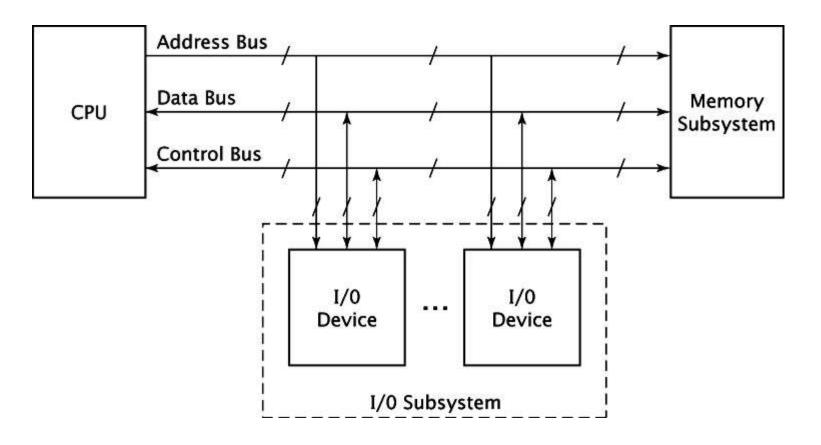

#### System Components

- CPU/Microprocessor

- Memory Subsystem

- I/O Subsystem

#### System Buses

- Address Bus

- Data Bus

- Control Bus

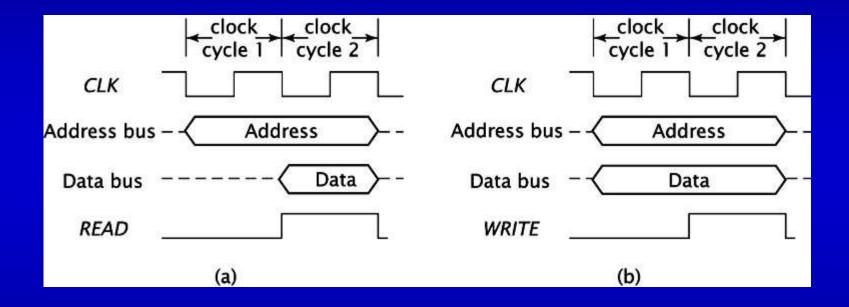

#### Instruction Cycle

- Fetch

- Decode

- Execute

#### **Instruction Fetch**

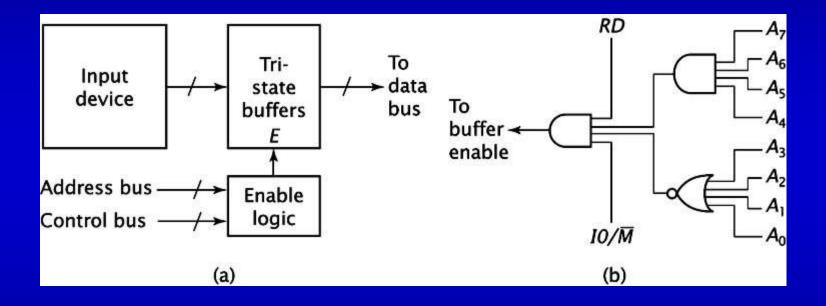

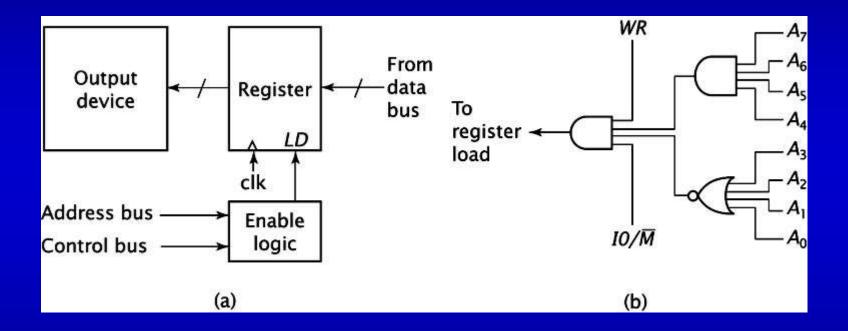

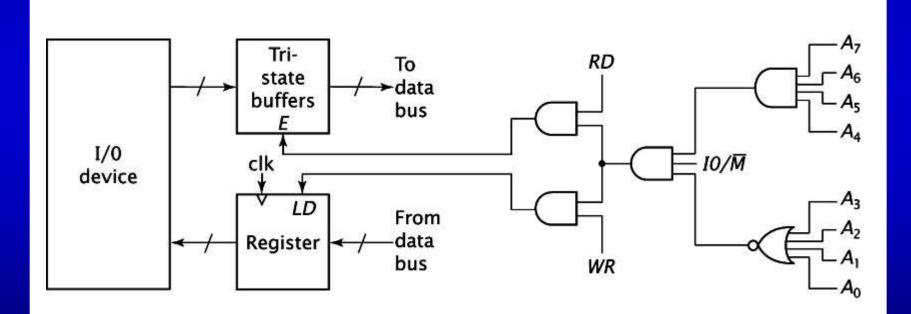

#### Types of I/O Organization

- Isolated I/O

- Memory-mapped I/O

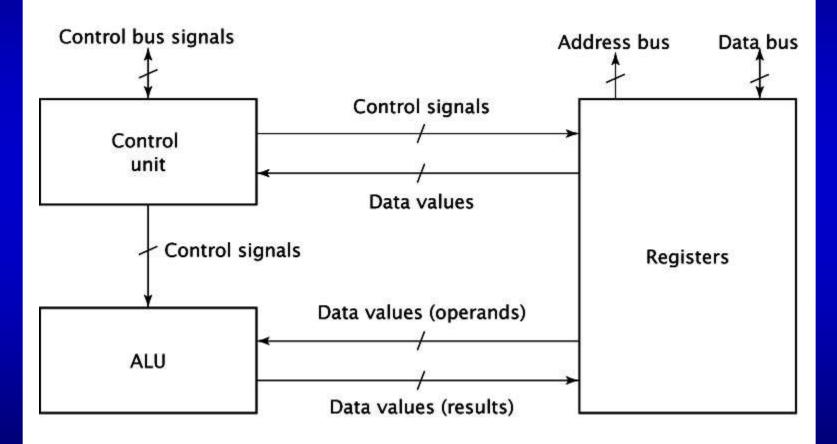

#### **CPU** Organization

#### **Types of Memory**

- Static RAM

- Dynamic RAM

- ROM

- PROM

- EPROM

- EEPROM

## KG REDDY College of Enclosed E

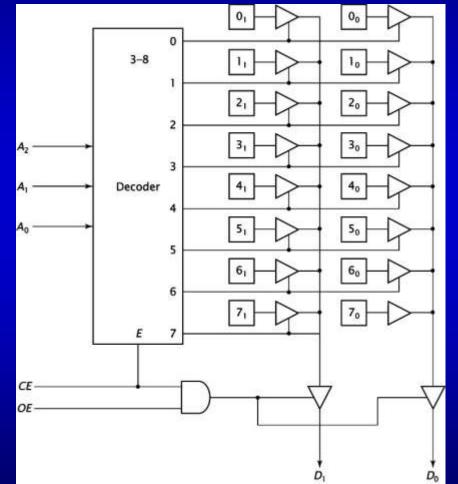

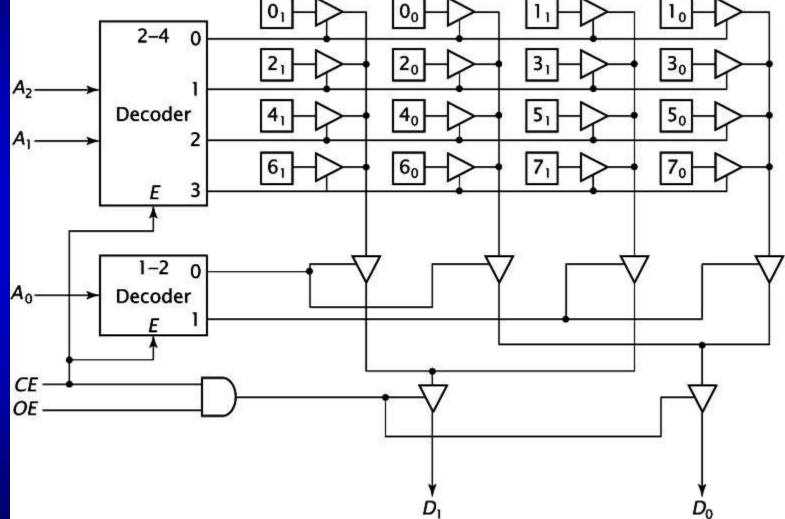

#### KGR Memory Chip Organization -Two Dimensional

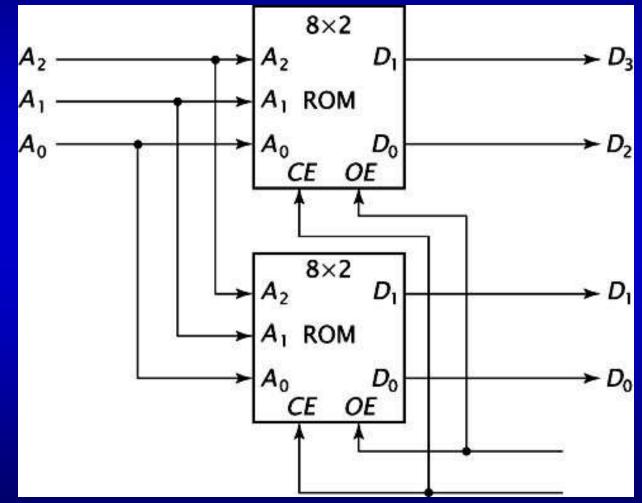

#### KG REDDY mbining Memory Chips to Increase Word Size

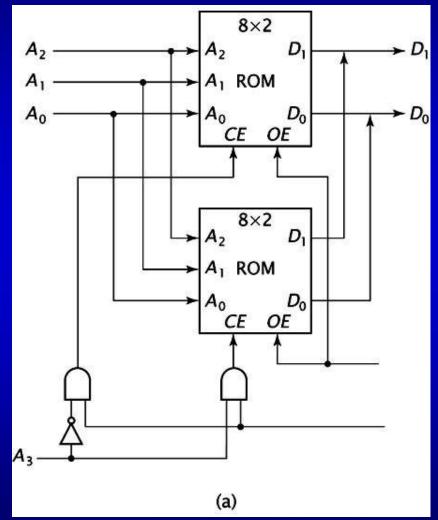

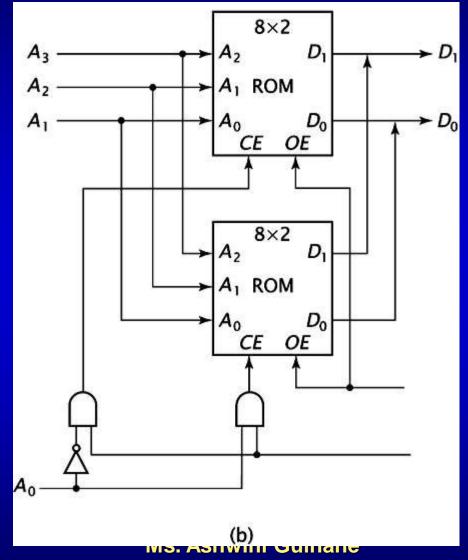

#### KGROCOMBINING Memory Chips to Increase Address Space

#### KG REDDY Low-order Interleaving College of Engineering

& Technology

#### von Neumann Architecture

- Instructions and data mixed

- Used in modern computers

#### Harvard Architecture

- Instructions and data separate

- Used in low-level cache memory design

Most significant byte first

| Memory Address | Data (in hex) |

|----------------|---------------|

| 100            | 01            |

| 101            | 02            |

| 102            | 03            |

| 103            | 04            |

#### Little Endian Data Organization • Least significant byte first

| Memory Address | Data (in hex) |

|----------------|---------------|

| 100            | 04            |

| 101            | 03            |

| 102            | 02            |

| 103            | 01            |

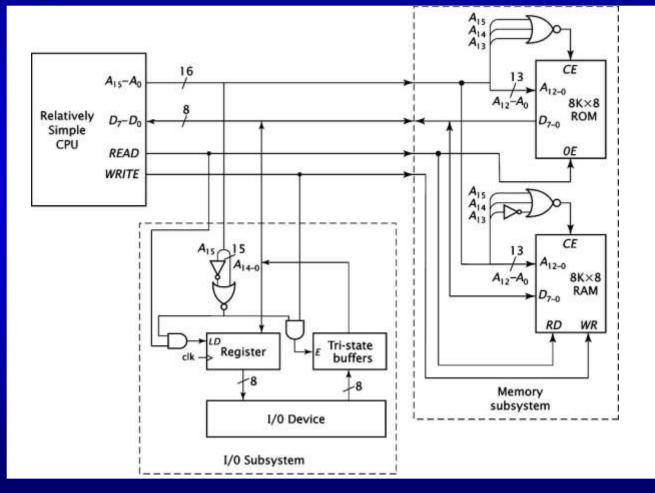

#### Input Device Organization

#### Output Device Organization

#### Bidirectional I/O Device Organization

- READY signal

- Interrupts

- DMA

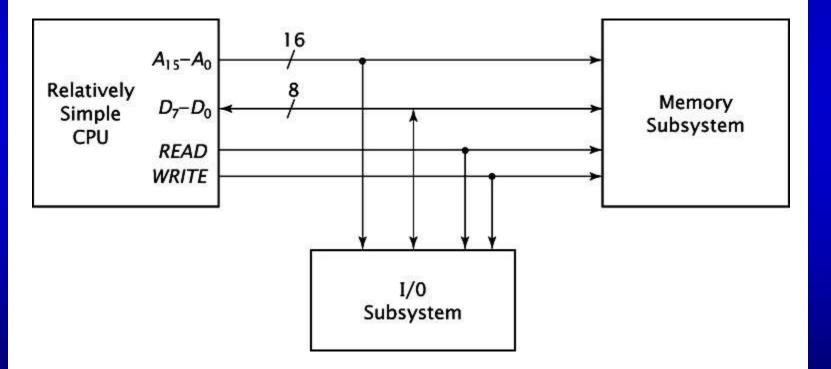

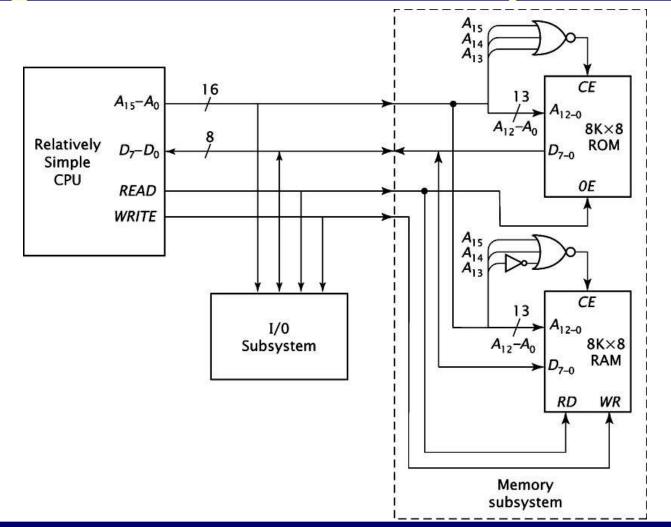

## Relatively Simple Computer Specifications

- Relatively Simple CPU

- 8K ROM starting at 0000H

- 8K RAM starting at 2000H

- Memory-mapped, bidirectional I/O port at 8000H

#### Relatively Simple Computer Organization - CPU Details

WS. ASHWIIII Guinane

# Constant Simple Computer Organization - Memory Details

#### KGREDDY Relatively Simple Computer Organization - Final Design

#### INCLUDE EXTERNAL ANIMATION FROM JAVA SIMULATOR HERE

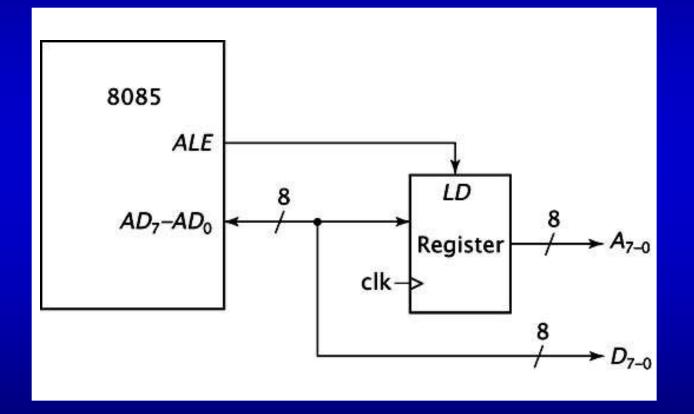

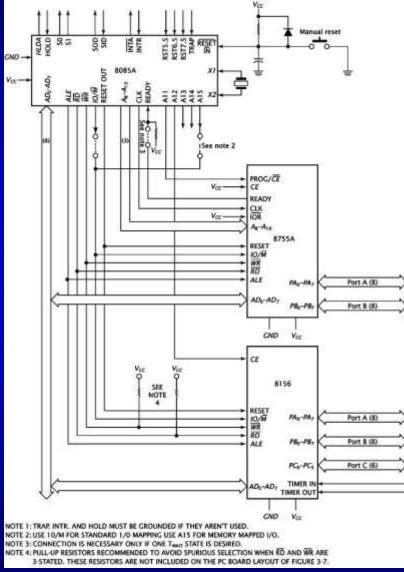

## 8085-based Computer Specifications

- 2K EPROM starting at 0000H

- 256 bytes RAM starting at 2000H

- Four 8-bit I/O ports at 00H, 01H, 19H, and 1AH

- One 6-bit I/O port at 1BH

# based Computer Organization

#### Summary

- Basic Computer Organization

- CPU Organization

- Memory Chip Internal Organization

- Memory Subsystem Organization

- I/O Port Organization and Interfacing